# Design and Development of Revolve Rescheduling Technique for Hash Event Blake Overshadowing Carry Select Adder thru Binary to Excess Converter

S. Ravichandran<sup>1</sup>, M. Umamaheswari<sup>2</sup> and R. Benjohnson<sup>3</sup>

<sup>1</sup>Research Scholar, Department of Computer Science, Bharathiar University, Coimbatore, India <sup>2</sup>Professor, Department of Information Technology, RRASE College of Engineering, Chennai, India <sup>3</sup>Assistant Professor, Department of Computer Applications, Coimbatore Institute of Management and Technology, Coimbatore, India E-mail: ravi17raja@gmail.com, karpagaravi15@gmail.com, benjohnsonr@gmail.com, druma\_cs@yahoo.com

E-mail: ravi1/raja@gmail.com, karpagaravi15@gmail.com, benjohnsonr@gmail.com, druma\_cs@yahoo.com (Received 23 June 2016; Revised 14 July 2016; Accepted 2 August 2016; Available online 10 August 2016)

Abstract - Cryptographic hash events remain consumed broadly appearing in numerous concentrations mostly for the situation high-pitched hustle then safety. NIST prepared SHA-3 struggle then the last ring-shaped contestants are BLAKE, KECCAK, SKEIN, JH THEN GROSTL. Amongst the five contestants enterprise besides planning of BLAKE remains evaluated in this manuscript. Hash event BLAKE remains the single-way cryptography which requires no key is consumed though referring and getting the communication. Inside the area of cryptography swiftness and privacy are the transactions. To achieve excessive swiftness then proficiency, Circumnavigate Reorganizing Procedure remains combined. Toward create BLAKE additional proficient, flexible calculation is swapped through Carry Select Adders (CSA) consuming Binary amongst the five contestants enterprise besides planning of BLAKE remains evaluated in this manuscript. Hash event BLAKE remains the single-way cryptography which requires no key is consumed though referring and getting the communication. Inside the area of cryptography swiftness and privacy are the transactions. To achieve excessive swiftness then proficiency, Circumnavigate Reorganizing Procedure remains combined. Toward create BLAKE additional proficient, flexible calculation is swapped through Carry Select Adders (CSA) consuming Binary to Excess Converter (BEC). The surviving then future design of BLAKE is invented consuming CSA while altered BLAKE is intended consuming CSA through BEC. Therefore, the range and capacity devoted in future technique is fewer evaluated thru surviving techniques. BLAKE-32, 64 remain implied in VHDL language then replicated in Modalism. Range and Capacity consequences remain exposed here Xilinx ISE simulant.

*Keywords:* HashEvent, SHA-3, NISTCSA, BEC, VHDL, Xilinx ISE simulant

# **I.INTRODUCTION**

Cryptography is probably the finest important highlight of organizations security subsequently continuous making progressively important equally an easy emergent piece aimed at terminal security. The supplemented procedure of workspace moreover communication structures concluded manufacturing consumes augmented the threat of thievery of registered communication. While these terrorizations can need a variation of pledge events, encryption remains an initial technique of shielding valued automated communication. The situation is an ability of organizing communications, hence that they convert incomprehensible. Now province of cryptography hashes obligate requests treatments with the conception of confirmation instructions, numerically passing manuscripts then invention of statically arbitrary information torrents. Hash events have no key then the plaintext is not recoverable from cipher text. A function that maps a variable -length data or message into a fixed length valve called a hash code. The function is designed such a way that when protected it provides an authenticator to the data or message. Also it is referred to as a message digest. For example person's name having a variable length could be hashed to a single integer. The ultimate purpose of a hash function is to produce a "finger print" of a file, message or other blocks of data and it should be collision free. The National Institute of Standards and Technology (NIST) have established a set of standardized hash functions called the Secure Hash Algorithm (SHA). The first version is SHA-0 and then consecutively SHA-1, SHA-2 and SHA-3 versions are introduced to provide additional security. NIST announced a global competition to find a new SHA function in 2007 and submissions were accepted for approximately one year. Totally 64 submissions are received out of which 51 were accepted as first round candidates and 14 as second round candidates in 2009. They are BLAKE, Blue midnight wish, Cube hash, Echo, Fugue, Grostl, Hamsi, JH, Keccak, Luffa, Shabal, SHA vite-3, SIMD, Skein[8]. The final round candidates are announced in 2010 as BLAKE, Grostl, JH, Keccak and Skein. The algorithms are being analyzed and narrowed down through elimination rounds, based on Security, Performance and Design of each function. In this paper SHA-3 finalists BLAKE is analyzed with its design, Architecture and its Performance. BLAKE obtains high speed and security apart from other finalists. Our work extends by replacing the modular addition in rescheduled G function with carry select adders using BEC, so that the power and area occupancy is less when compared with the existing work.

# **II.BLAKE DESCRIPTION**

BLAKE has two main versions such as BLAKE-32 and BLAKE-64. Complete specifications are given below.

# A. BLAKE-32 and BLAKE-64

The BLAKE-32 algorithm operates on 32-bit words and returns a 256-bit hash value, whereas BLAKE-64 operates on 64- bit words and returns a 512-bit hash value Length of all variables is doubled when compared to BLAKE-32. The compressive function of BLAKE-64 is similar to BLAKE-32. That it makes 14 rounds instead of t e n, and uses rotation distances as 32,25,16,11. After ten rounds, the round function uses the permutations  $\sigma_0...\sigma_3$  for the last four rounds. It's based on the compressive function. This function is decomposed into 3 main parts such as Initialization, Round function and Finalization. The compressive function of BLAKE -32 has four values as its input. Chaining value h = h\_0 .....h7

Message block  $m = m_0 \dots m_{15}$ Salt  $s = s_0 \dots s_3$ Counter  $t = t_0, t_1$

The input salt is an optional one which is used only for specific applications such as randomized hashing [6]. The output obtained from the compressive function is new chaining value  $h' = h'_0 \dots h'_7$  of 256 bits.

#### 1. Initialization

V0...V15 initial state is represented in a 4 \*4 matrix of 32-bit words. Initialization vector used by BLAKE-256 is given below.

| IV = 6A09E667 |

|---------------|

| IV = BB67AE85 |

| IV = 3C6EF372 |

| IV = A54FF53A |

| IV = 510E527F |

| IV = 9B05688C |

| IV = 1F83D9AB |

| IV = 5BE0CD19 |

Within the compress function, a 512-bit state v is maintained, treated as a 4x4 matrix of 32-bit words. This state is initialized from the current hash, salt value, timer value t, and a 256-bit constant c. The initial state of the compression function is given.

| fh0             | h1     | h <sub>2</sub> | h3             | ٦  |

|-----------------|--------|----------------|----------------|----|

| h4              | h5     | h6             | h7<br>⊕c2 s3⊕c |    |

| <sub>s0</sub> € | Dc0 si | 1 ⊕c1 s2 €     | ⊕c2 s3⊕c       | :4 |

| t0 (            | ⊕c4    | t1 ⊕c5 t2      | ⊕c6 t3⊕        | c7 |

| t               |        |                |                | )  |

Where c0 .... C15 are predefined word constants. The digits of constant c are directly taken from the hexadecimal representation of  $\pi$ , chosen for its irrational nature as shown below.

| $c_0 = 243F6A88$  | $c_1 = 85A308D3$    |

|-------------------|---------------------|

| $c_2 = 13198A2E$  | $c_3 = 03707344$    |

| $c_4 = A4093822$  | $c_5 = 299F31D0$    |

| $c_6 = 082 EFA98$ | c7 = EC4E6C89       |

| $c_8 = 452821E6$  | c9 = 38D01377       |

| c10= BE5466CF     | $c_{11} = 34E90C6C$ |

| c12= C0AC29B7     | $c_{13} = C97C50DD$ |

| c14= 3F84D5B5     | $c_{15} = B5470917$ |

After initializing the state matrix, it's iteratively processed through 14 rounds. In designing BLAKE less complicate rounds are suggested and absolutely proven to provide greater security. Such as security which means it's difficult to invert such that function inputs cannot be determined from function outputs.

## **2. Round Function**

Every round contains of eight state alterations, marked G0 across G7. These are dependable for the confusion (changes to data) and diffusion (dispersion of data) of the BLAKE algorithm. A round is a transformation of the state that computes,

| G <sub>0</sub> (V <sub>0</sub> , V <sub>4</sub> , V <sub>8</sub> , V <sub>12</sub> ) | G <sub>1</sub> (V <sub>1</sub> , V <sub>5</sub> , V <sub>9</sub> , V <sub>13</sub> )  |

|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| G <sub>2</sub> (V2, V <sub>6</sub> , V <sub>10</sub> , V <sub>14</sub> )             | G <sub>3</sub> (V <sub>3</sub> , V <sub>7</sub> , V <sub>11</sub> , V <sub>15</sub> ) |

| G4 (V0, V5, V10, V15)                                                                | G5 (V1, V6, V11, V12)                                                                 |

| G <sub>6</sub> (V2, V7, V8, V13)                                                     | G7 (V3, V4, V9, V14)                                                                  |

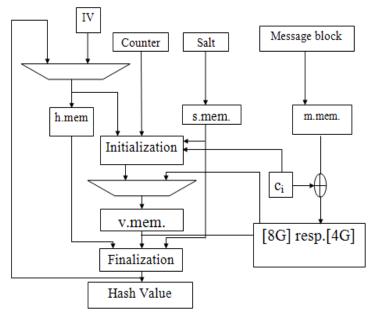

Each operates on and modifies only by 4 of the 16 state words which is generalized as a, b, c and d. this transformation consists of addition, bit rotation and XOR operations. The main architecture of BLAKE is shown in Figure 1.The general G transformation for BLAKE-64 is given by,

$\begin{array}{l} a < ---- \ a + b(m_{GT}(2i) \ \bigoplus \ c_{GT}(2i+1)) \\ d < ---- \ (d \ \bigoplus \ a) >>> 32 \ c < ---- \ c+d \\ b < ---- \ (b \ \bigoplus \ c) >>> 25 \\ a < ---- \ a + b + \ (m_{GT} \ (2i+1) \ \bigoplus \ c_{GT} \ (2i)) \\ d < ---- \ (d \ \bigoplus \ a) >>> 16 \ c < ---- \ c+d \\ b < ---- \ (d \ \bigoplus \ a) >>> 11 \end{array}$

Fig.1 Main Architecture of BLAKE

$\sigma_r$  refers to permutation s from 0 to 9. The permutation table for BLAKE is shown in following table respectively.

| σ0         | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| σ1         | 14 | 10 | 4  | 8  | 9  | 15 | 13 | 6  | 1  | 12 | 0  | 2  | 11 | 7  | 5  | 3  |

| σ2         | 11 | 8  | 12 | 0  | 5  | 2  | 15 | 13 | 10 | 14 | 3  | 6  | 7  | 1  | 9  | 4  |

| σ3         | 7  | 9  | 3  | 1  | 13 | 12 | 11 | 14 | 2  | 6  | 5  | 10 | 4  | 0  | 15 | 8  |

| σ4         | 9  | 0  | 5  | 7  | 2  | 4  | 10 | 15 | 14 | 1  | 11 | 12 | 6  | 8  | 3  | 13 |

| σ5         | 2  | 12 | 6  | 10 | 0  | 11 | 8  | 3  | 4  | 13 | 7  | 5  | 15 | 14 | 1  | 9  |

| <b>σ</b> 6 | 12 | 5  | 1  | 15 | 14 | 13 | 4  | 10 | 0  | 7  | 6  | 3  | 9  | 2  | 8  | 11 |

| <b>σ</b> 7 | 13 | 11 | 7  | 14 | 12 | 1  | 3  | 9  | 5  | 0  | 15 | 4  | 8  | 6  | 2  | 10 |

| <b>σ</b> 8 | 6  | 15 | 14 | 9  | 11 | 3  | 0  | 8  | 12 | 2  | 13 | 7  | 1  | 4  | 10 | 5  |

| σ9         | 10 | 2  | 8  | 4  | 7  | 6  | 1  | 5  | 15 | 11 | 9  | 14 | 3  | 12 | 13 | 0  |

TABLE 1 PERMUTATION TABLE FOR BLAKE

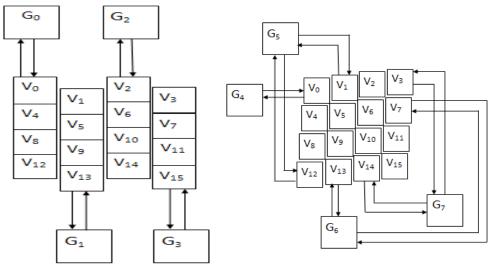

The state words on which each G transformation operates is that first four calls  $G0....G_3$  are computed in parallel and from G4 to G7 are computed diagonally. The

order  $G_{0}$ ...  $G_{3 is}$  called as column step and  $G_{4}$ ... $G_{7}$  as diagonal step. The parallelization is shown in the Figure 2.

Fig.2 Parallelized column step and Diagonal step

### 3. Finalization

After ten /14 rounds of G transformation the compressive function performs final step. Thus the n e w chaining value h' is extracted from state  $V_{0...}V_{15}$  with input of the chaining value h and salt S.

$h_0' = h_0 \text{ xor } s_0 \text{ xor } v_0 \text{ xor } v_8$   $h_1' = h_1 \text{ xor } s_1 \text{ xor } v_1 \text{ xor } v_9$   $h_2' = h_2 \text{ xor } s_2 \text{ xor } v_2 \text{ xor } v_{10}$   $h_3' = h_3 \text{ xor } s_3 \text{ xor } v_3 \text{ xor } v_{11}$   $h_4' = h_4 \text{ xor } s_0 \text{ xor } v_4 \text{ xor } v_{12}$   $h_5' = h_5 \text{ xor } s_1 \text{ xor } v_5 \text{ xor } v_{13}$   $h_6' = h_6 \text{ xor } s_2 \text{ xor } v_6 \text{ xor } v_{14}$  $h_7' = h_7 \text{ xor } s_3 \text{ xor } v_7 \text{ xor } v_{15}$

## **III.ROUND RESCHDULING METHOD**

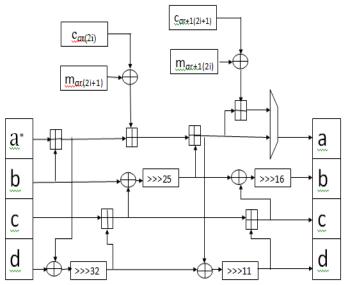

The G function of BLAKE is modified with round rescheduling technique. The introduction of the addition with message constant pair in the G function leads to an increment of the propagation delay. If in single call of G, each update of the state has been conceived to operate sequentially, the MC- pair addition can be shifted within the computations. It is thus possible to anticipate it, reducing the critical path of G. the rescheduled  $G_i$  (a\*, b, c, d) computes,

$\begin{array}{l} a:=a^{*}+b\\ d:=(d\bigoplus a)>>>r_{0}\end{array}$

c := c+d  $b := (b \bigoplus c) >>> r_1$   $a := a+b+ (m_{\sigma r}(2i+1) \bigoplus c_{\sigma r}(2i))$   $d := (d \bigoplus a) >>> r_2$  c := c+d  $b := (d \bigoplus a) >>> r_3$  $a^* := a+ (m_{\sigma r+1} (2i) \bigoplus c_{\sigma r+1} (2i+1))$

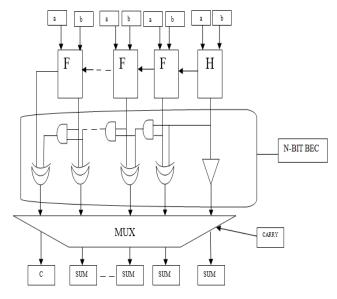

Where  $r_i$  are the rotation indices for BLAKE-32 and a<sup>\*</sup> corresponds to the modified first input/output variable after the MC addition. To keep the correct functional behavior, a two-input MUX should be inserted before the sequential logic, hence allowing the record of a instead of a<sup>\*</sup> in the last round. This is the main reason why the rescheduling optimization could not be carried out automatically by the synthesis tool and must be instantiated at code level. The rescheduled G transformations for BLAKE-64 are visually shown in following Figure3.

In this paper instead of normal modular addition carry select adder with BEC is used. So that the area occupied is less and power consumption is also less. When compared with other adders this CSA suits this technique and proves to be more efficient. Total rounds obtained for BLAKE-64 is 14 and for BLAKE-32 are 10. Round rescheduling technique is provided to speed up the process with high security and delay reduction.

Fig.3 Structural Diagram of the Rescheduled G function

### **IV.CARRY SELECT ADDERS USING BEC**

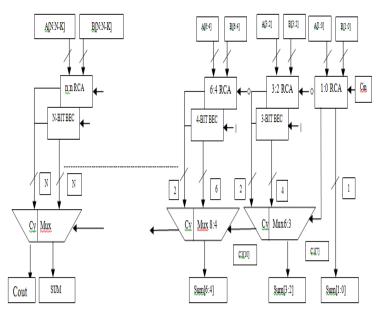

The sketch of BLAKE-32bit consuming CSA is displayed in Figure.4. Now it displays an adder with block dimensions of 2-2-3-4-5-6-7-3 bit. Every section has 2-2-3-4-5-6-7-3 bit Ripple Carry Adder (RCA) and multiplexer. Later carry-in is identified at the initiating of calculation, a carry select section is not required a mux meant for the first two bits. The drawback of ripple carry adder is that every adder has to stay for the coming of its carry-input signal earlier the real addition can begin. The essential impression of the Carry-Select Adder is to consume blocks of two Ripple-Carry Adders, one of which is supported with a coefficient 0 carry-in while the other is supported with a coefficient 1 carryin. Hence, together sections are able to estimate in resemblance. When the real carry-in signal for the section reaches, multiplexers are consumed to select the right one of together pre computed incomplete sums. Moreover, the occasioning carry-out is designated and promulgated to the subsequently carry-select block.

However, the CSA is not area efficient because it uses multiple pairs of ripple carry adders(RCA) to generate partial sum and carry by considering carry input cin=1 and cin=0,then the final sum and carry are selected by the multiplexers (mux) which means, the whole blocks has contains so many full adders of RCA. The ripple carry adder has requires more number of logic gates for addition operation. Area for each one of full adder is 13 and area for each one of 2:1 mux is 4.

Fig.4 Layout of BLAKE consuming CSA with BEC

So that it occupies more area in the regular CSA. The CSA have also required more power and it is not area efficient. In order to overcome these demerits, modification CSA is designed. That is add a BEC -1 instead of RCA with cin=1. Carry select adder is not area efficient; because of number of ripple carry adders are present in each block. Therefore, the carry select adder is modified by replacing BEC structure instead of RCA with cin=1. The logic gates are reduced by this modification. By this modification we may be achieve reduce delay and total area size.

BEC is a non-weighted code. It is also a selfcomplementing BCD code used in decimal arithmetic units. The Excess-1 code for the decimal number is performed in the same manner as BCD except that decimal number 1 is added to the each decimal unit before encoding it to binary. The main idea of this work is to use BEC instead of the RCA with cin=1 in order to reduce the area and power consumption of the regular CSA. The importance of the BEC logic stems from the large silicon area reduction when the CSA with large number of bits are designed. To replace the n-bit RCA, an n+1 bit BEC is required. A structure and the function table of an n-bit BEC are shown in Figure5.

Fig.5 Organization of N-BIT BEC

The Boolean expressions of the 4-bit BEC is scheduled as (note the practical pictograms ~NOT, &AND, ^XOR).

X0=~B0 X1=B0^B1 X2=B2^(B0&B1) X3=B3^(B0&B1&B2) C1=B3&B2 C2=B0&B1 C0=C1&C2

## V.IMATIOIN WORK & COMPARISION RESULTS

Aimed at the simulation work in this manuscript to accept VHDL language and simulated in Modalism and

additionally manufactured in XILINX ISE simulator. The Area and Delay, Power costs were achieved from the XILINX ISE simulator.

Figure 6 and 7 displays the pictures of simulation window. Memorandum, hash, salt, counter are the keys and hd0.. hd7 are the last hash valve. Outstanding costs shown in the pictures are the signals\_clk is comprised to acquire the power statement. Modified BLAKE-32, 64 using carry select adders with BEC is displayed under.

The proportional effects of BLAKE-32, 64 consuming CSA with BEC for Surviving, Future and Altered are showed evidently in the subsequent table.

| Messages            |                |                                             |

|---------------------|----------------|---------------------------------------------|

| /blake32/clk        | 1              |                                             |

| ▪→ /blake32/message | 01000001011101 | 010000010111011001101001011011100110000101  |

| ▪-                  | 01000101011001 | 01000101011001000111010101000110110000101   |

|                     | 01101111011001 | 011011110110011001000011011100100111100101  |

| ▪→ /blake32/counter | 01000110011101 | 0100011001110101011011100110110001110100011 |

| ▪ /blake32/hd0      | C08BD8EF       | C08BD8EF                                    |

| 🖅 /blake32/hd1      | DC018003       | DC018003                                    |

|                     | 3CCFA9DD       | 3CCFA9DD                                    |

| ▪ /blake32/hd3      | C98D8B95       | C98D8B95                                    |

|                     | 3058E3A5       | 3058E3A5                                    |

|                     | AF7B5FD0       | AF785FD0                                    |

|                     | 49EB7467       | 49EB7467                                    |

| 🖅 /blake32/hd7      | 57DED132       | 57DED132                                    |

| ▪ /blake32/h0       | 45647563       | 45647563                                    |

| ▪ /blake32/v0       | E419A78F       | E419A78F                                    |

|                     |                |                                             |

| A R O Now           | 28000 ns       | 27500 ns 28000 r                            |

| Ga∕e Cursor 1       | 0 ns           |                                             |

|                     | •              |                                             |

|                     |                |                                             |

Fig.6 Adapted BLAKE-32 consuming CSA with BEC

| Messages                                     |                            |                                             |

|----------------------------------------------|----------------------------|---------------------------------------------|

| 🔷 /blake64/clk                               | 1                          |                                             |

|                                              | 01000001011101             | 010000010111011001101001011011100110000101  |

| 🖅 🔶 /blake64/hash                            | 01000010011101             | 0100001001110100101101110011000010111001001 |

|                                              | 01001000011000             | 0100100001100001011100100110010001110111011 |

| 🖅 🔶 /blake64/counter                         | 01000011011000             | 010000110110000101110010011100100111100101  |

|                                              | 067602675953C6             | 067602675953C6BD                            |

| 🗉 🧇 /blake64/hd1                             | C9C278B2E4D738             | C9C278B2E4D7388E                            |

|                                              | DA63F044FFCFF8             | DA63F044FFCFF83D                            |

| 🗉 🍫 /blake64/hd3                             | 113F7DAB0FEA77             | 113F7DAB0FEA77D4                            |

|                                              | D4DCAF020650E6             | D4DCAF020650E6B2                            |

|                                              | F606362A2BAB05             | F606362A2BAB0583                            |

|                                              | B8EC7CB690497F             | B8EC7CB690497F67                            |

| 🗉 🤣 /blake64/hd7                             | FBECA69F7DCC7              | FBECA69F7DCC7198                            |

|                                              | 4274B730B93CBA             | 4274B730B93CBA37                            |

|                                              | B9C8417FF0AA96             | B9C8417FF0AA9648                            |

|                                              |                            |                                             |

| A R O Now                                    | 47600 ns                   | 47000 ns 47500 ns                           |

| 🗟 🎤 🥥 🛛 Cursor 1                             | 0 ns                       |                                             |

| <b>∢</b>                                     | •                          |                                             |

| <ul> <li>/blake64/v0</li> <li>Now</li> </ul> | 89C8417FF0AA96<br>47600 ns |                                             |

Fig.7 Adapted BLAKE-64 consuming CSA with BEC

| WORD<br>SIZE | HASH<br>FUNCTION<br>BLAKE   | AREA   | POWER |  |

|--------------|-----------------------------|--------|-------|--|

|              | PREVAILING<br>CSA           | 15,762 | 73    |  |

| 32           | PLANNED<br>CSA              | 13,100 | 68    |  |

|              | ADAPTED<br>CSA USING<br>BEC | 6282   | 52    |  |

|              | PREVAILING<br>CSA           | 17,550 | 84    |  |

| 64           | PLANNED<br>CSA              | 18,136 | 81    |  |

|              | ADAPTED<br>CSA USING<br>BEC | 9757   | 60    |  |

# **VI.CONCLUSION**

In this manuscript the Performance and Design of BLAKE is analyzed thoroughly. Also how round rescheduling technique is incorporated in hash function BLAKE is shown clearly. The comparative study of area and power report is shown in table. To make BLAKE more efficient carry select adders are used so that the power consumption is low when compared to other adders. In case of binary to excess converter reduces the gate counts and occupies less area. The major concerns of the VLSI designer were area, performance, cost and reliability. Power consideration was mostly of one secondary importance. Designers of next generation systems want to integrate more features and get higher performance within or smaller area and power budget. the same Furthermore, some applications like signal processing, wireless network, intelligent control, etc. have specific power requirements that must be adhered to in order to be compliant with system specifications and standards.

# ACKNOWLEDGMENT

The authors are thankful to Padma Devi, T.Y.Ceiang, M.J.Hsiao and my guide for providing the necessary facilities for the preparation of the paper. Also thanks to AJIST staffs to publish this paper. At last, I extend my heartfelt salutations to our beloved Parents, my Wife and to the almighty to establish this paper in successful manner.

### REFERENCES

- [1] SHA-1 Standard, National Institute of Standards and Technology (NIST), Secure Hash Standard, FIPS PUB 180-1,International Journal of Computer Trends and Technologyvolume3Issue2- 2012, ISSN: 2231-2803 Page 272 1995, available on line at www.itl.nist.gov/fipspubs/ fip180-1.html

- [2] J.-P. Aumasson, L. Henzen, W. Meier and R.C.-W Phan, "SHA-3 Proposal BLAKE, submission to NIST," 2008. [Online]. Available:http://131002.net/blake/

- [3] Cryptanalysis of Dynamic SHA 2 by Jean-philipe, Orr Dunklemen, Bart Preneel Sabastian Indesteege.

- [4] Paul F.Stelling, "Design strategies for optimal hybrid final adders in parallel multiplier", Journal of VLSI signal processing, vol 14, pp. 321-331, 1996.

- [5] T.Y.Ceiang and M.J.Hsiao, "carry-select adder using single ripple carry adder," Electron .Lett., vol.34, no.22,pp.2101-2103, oct. 1998.

- [6] K.Rawwat, T.Darwish and M. Bayoumi, "A low power carry select adder with reduces area," proc. of Midwest Symposium on Circuits and Systems, pp.218-221, 2001.

- [7] Padma Devi, Ashima Girdhar and Balwinder Singh "Improved carry select adder with Reduced Area and low power consumption" Int Jou of Com Appl(0975-8887) vol3- no.4, June 2010.

- [8] Luca Henzen, Pietro Gendotti, Patrice Guillet, Enrico Pargaetzi, Martin Zoller, and Frank K. Gurkaynak. Developing a hardware evaluation method for sha-3candidates. In Mangard and Standaert [21], pages 248{263.

- [9] Xu Guo , Meeta Srivastav , Sinan Huang , Leyla Nazhandali and Patrick Schaumont Silicon Implementation of SHA-3 Final Round Candidates: BLAKE, Gr\_stl, JH, Keccak and Skein dec. 2009,

- [10] National Institute of Standards and Technology (NIST). Cryptographic Hash Algorithm Competition Website. http://csrc.nist.gov/groups/ST/hash/sha-3

- [11] NIST, Gaithersburg, MD, "Announcing the secure hash standard," FIPS180-2, 2002.

- [12] NIST, Gaithersburg, MD, "SP 800-106, randomized hashing digital signatures," 2007

- [13] X. Wang and H. Yu, "How to break MD5 and other hash functions," in Advances in Cryptology—EUROCRYPT 2005, ser. Lecture Notes in Computer Science. Berlin, Germany: Springer, 2005, vol. 3494, pp. 19–35.

- [14] L. Ji and X. Liangyu, "Attacks on round-reduced BLAKE," 2009